In this use case, the customer maps a hardware design onto an FPGA. LitenAI assists with design, architecture, and debugging flow issues. It consolidates manuals, debug information, support data, and logs into its Smart Data Lake, enabling intelligent searches and detailed analysis. The LitenAI Agent uses this data to deliver precise technical support. Based on the user prompt, the appropriate agent is activated to address the request.

See below for an example of this flow. In an FPGA flow, smart lake contains all the manuals as well as log files produced by synthese, place and route flows. This tool can assist with design flow and debug as shown below.

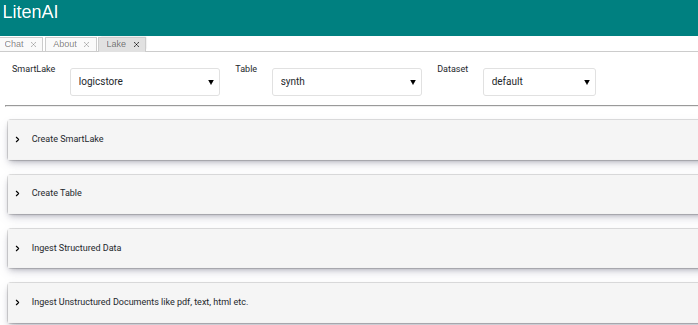

Smart Lake

In the LitenAI Smart Lake tab, select the logicstore Smart Lake. It includes ingested FPGA manuals, along with example synthesis and placement/routing log files.

LitenAI Agents

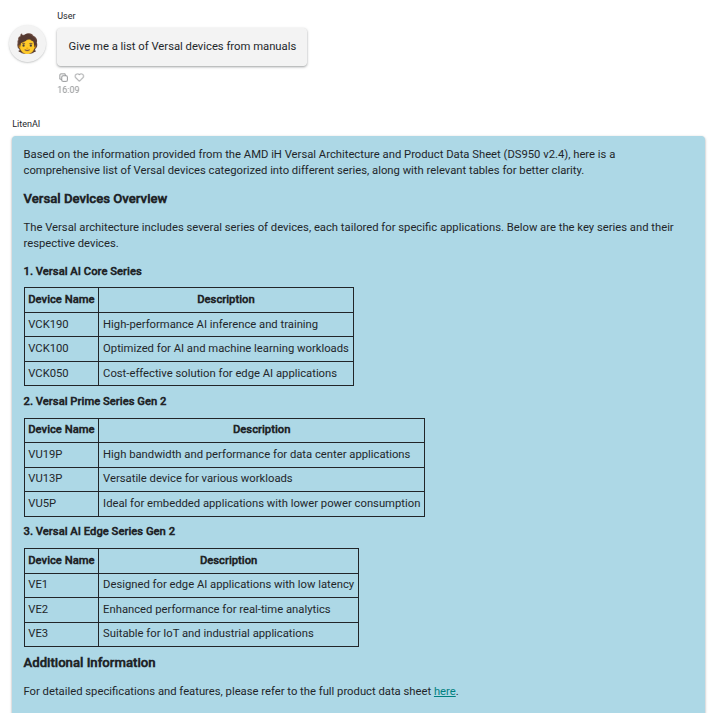

Customers can inquire about Versal devices, with answers retrieved from the Smart Lake for greater accuracy and detail than ChatGPT.

Give me a list of Versal devices from manuals?

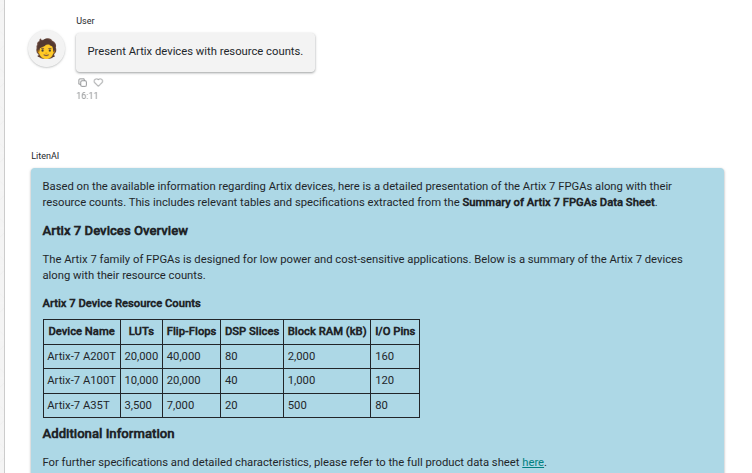

Present Artix devices with resource counts.

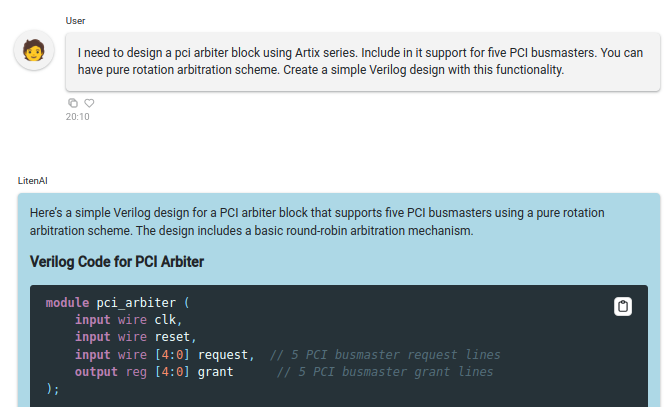

LitenAI can generate a Verilog design block for a simple design. It ensures accuracy by grounding the design in verified information from its Smart Lake and agents.

I need to design a pci arbiter block using Artix series. Include in it support for five PCI busmasters. You can have pure rotation arbitration scheme. Write verilog RTL to create the design using ask.

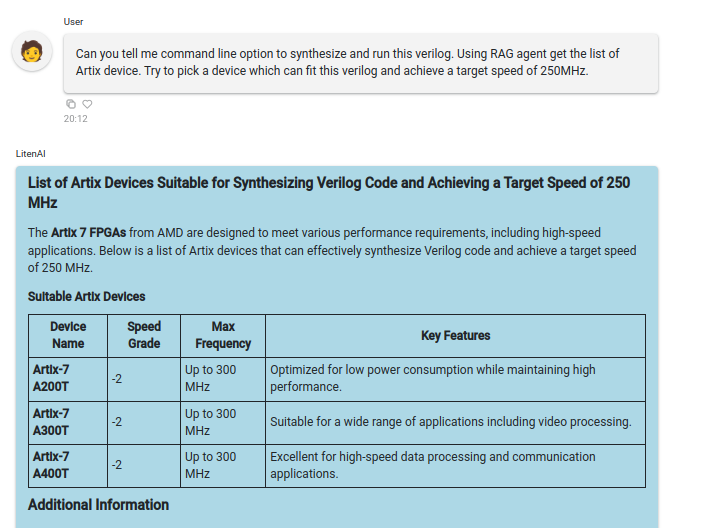

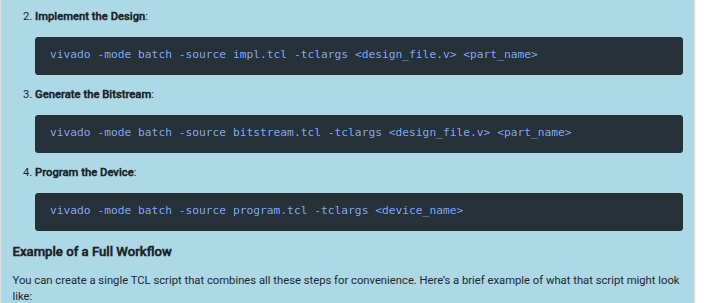

Since Smart Lake has ingested the manuals, it can provide the required command lines for implementations.

Can you tell me command line option to synthesize and run this verilog. Using RAG agent get the list of Artix device. Try to pick a device which can fit this verilog and achieve a target speed of 250MHz.

Command line prompts are also shown.

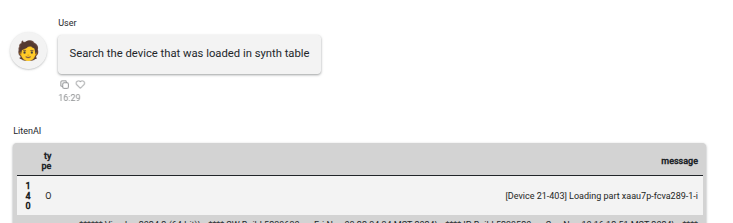

Tool log analysis

LitenAI Smart Lake now contains sample synthesis and place/route logs, enabling detailed analysis and debugging.

Search the device that was loaded in synth table.

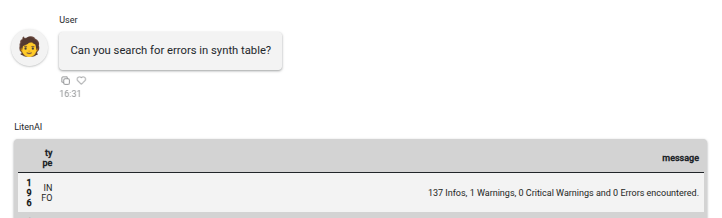

Search for errors in the logicstore.synth table.

Synthesis completed successfully with no errors found in the synth table.

You can also analyze place and route logs. It can then be analyzed for any error conditions.

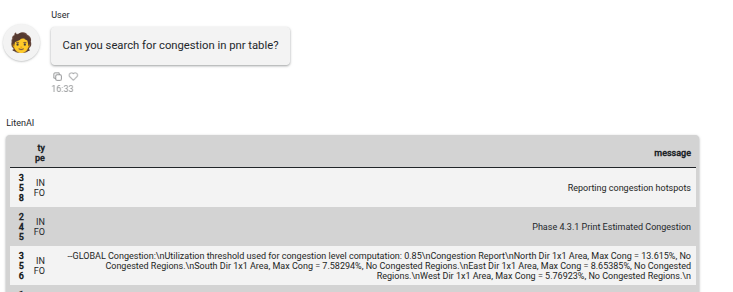

Search for congestion in logicstore.pnr table. Use congestiondata dataset name for output.

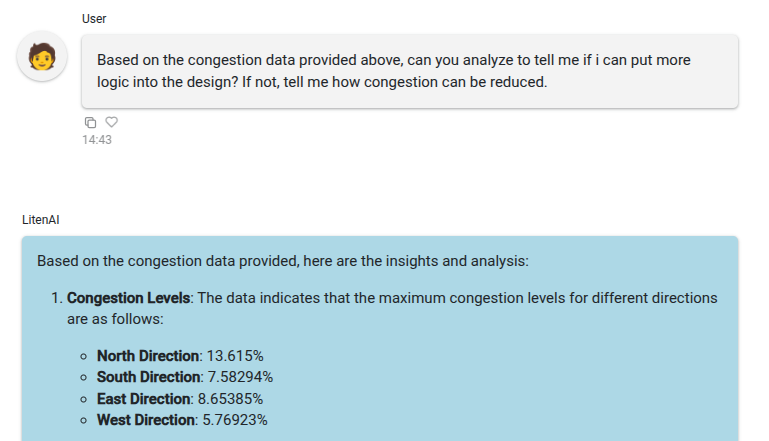

Based on the congestion data in dataset congestiondata , can you analyze to tell me if i can put more logic into the design? If not, tell me how congestion can be reduced.

This flow shows how a hardware design flow can be performed and debugged using LitenAI platform.